On the way to the Synkie-Delay

You are viewing an old revision of this post, from October 26, 2013 @ 09:19:21. See below for differences between this version and the current revision.

We already did several attempts over the last 3 years to build a video delay module for the Synkie – somehow it’s odd: the whole idea of the Synkie is to get rid of latency when doing live visuals, and then we try hard to bring back some latency into the system…

But a controllable, variable means to delay the signal is sort of the holy grail for me and will open a lot of potential…

To build a delay we have to sample the signal ( at minimum 10 Mhz), store the samples in RAM read them out some time later and convert back to analog. Until now we were not able to build a circuit that creates the necessary control signals in a correct manner . We also tried to use static RAM, because it seemed simpler to interface than dynamic RAM which should be initialized properly and refreshed periodically .

Complex signals on a very tight schedule – we needed some programmable logic to act as a controller for the different parts of the system:

So over the last year I dove into VHDL programming and spent several weeks just trying to install the vendor specific development tools. It’s a strange and bizarre world, with industry heavyweights just trying you to sell you their IP for hard $$$$$ through complex and completely counterintuitive software that weighs in at tens of gigabytes.

I started with Lattice CPLDs. I bought a cheap Laptop to get a clean Windows system, installed their whole suite but then ran into trouble, somehow fried the small development board before I could run my first code on it. Can’t remember the details anymore. Switched to Xilinx – installed their huge ISE Webpack, found out how to simulate and stuff but never managed to program a board. And Microsoft Windows freaks me out.

The last FPGA workshop I attended at dock18 used Altera FPGAs, so I spent another weekend installing all their tools, this time in a virtual machine on my Macbook running Ubuntu Linux 12.3 – now I’m able to do all my editing in BBEdit on the Mac where I’m at home, and just compile and simulate in the shared folder on the linux side of things.

I’m quite happy with this setup, and best of all: It actually works!

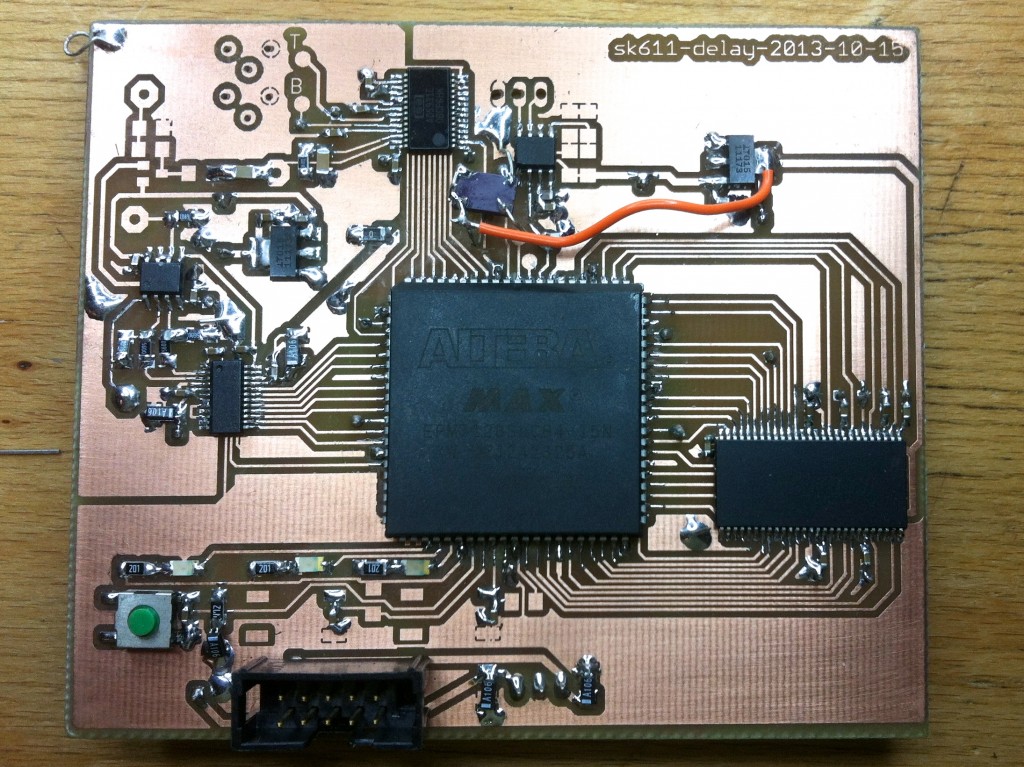

Built a first prototype board, downloaded my first VHDL via JTAG and the thing actually displays some delayed out of sync video signal – although in very bad quality over the live signal at the same time. there seems to be some bus contention on the bidirectional data bus between the cold and the sdram.

Version 1 of CPLD-driven video delay.

Version 1 of CPLD-driven video delay.

The DS1077 I used to generate a 133 Mhz clock is WAY to jittery, the clock drifts too much: wobbly lines through the picture. tried to use a quartz oscillator but now nothing ticks anymore 🙁 Anyway the CPLD is too small to fit all the functions I want – will do another prototype with a MAXII…

more to come

Module Info

| Inputs: | |

|---|---|

| Outputs: | |

| Power Draw on +5V: | N/A |

| Power Draw on -5V: | N/A |

| Frequency Response: |

Schematic & PCB

Observations

No observations yet

Revisions:

- October 26, 2013 @ 09:19:21 [Current Revision] by Michael

- October 26, 2013 @ 09:19:21 by Michael

- October 25, 2013 @ 08:02:09 by Michael

Changes:

There are no differences between the October 26, 2013 @ 09:19:21 revision and the current revision. (Maybe only post meta information was changed.)